# P4C1041 HIGH SPEED 256K x 16 (4 MEG) STATIC CMOS RAM

### **FEATURES**

- High Speed (Equal Access and Cycle Times)

10/12/15/20 ns (Commercial)

12/15/20 ns (Industrial/Military)

- Low Power

- Single 5.0V ± 10% Power Supply

- 2.0V Data Retention

- Easy Memory Expansion Using CE and OE Inputs

- Fully TTL Compatible Inputs and Outputs

- Advanced CMOS Technology

- Fast t<sub>oe</sub>

- Automatic Power Down when deselected

- Packages —44-Pin SOJ, TSOP II

### DESCRIPTION

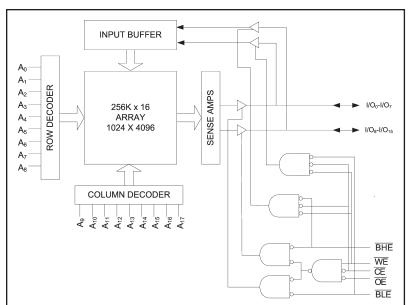

The P4C1041 is a 262,144 words by 16 bits high-speed CMOS static RAM. The CMOS memory requires no clocks or refreshing, and has equal access and cycle times. Inputs are fully TTL-compatible. The RAM operates from a single  $5.0V \pm 10\%$  tolerance power supply.

Access times as fast as 10 nanoseconds permit greatly enhanced system operating speeds. CMOS is utilized to reduce power consumption to a low level. The P4C1041 is a member of a family of PACE RAM<sup>™</sup> products offering fast access times. The P4C1041 device provides asynchronous operation with matching access and cycle times. Memory locations are specified on address pins  $A_0$  to  $A_{17}$ . Reading is accomplished by device selection ( $\overline{CE}$  and output enabling ( $\overline{OE}$ ) while write enable ( $\overline{WE}$ ) remains HIGH. By presenting the address under these conditions, the data in the addressed memory location is presented on the data input/output pins. The input/output pins stay in the HIGH Z state when either  $\overline{CE}$  or  $\overline{OE}$  is HIGH or  $\overline{WE}$  is LOW.

Package options for the P4C1041 include 44-pin SOJ and TSOP packages.

PIN CONFIGURATION

$A_0 \square$

A1 🗆

$A_3 \square$

$A_2 \square 3$

A₄ 🗖 5

I/O1 🗖 8

I/O3 🗖 10

V<sub>cc</sub> - 11

V<sub>SS</sub> [ 12

I/O<sub>4</sub> 🗖 13

I/O<sub>5</sub> 🗖 14

I/O<sub>6</sub> 🖂 15

I/O7 🗖 16

WE 🗖 17

A<sub>6</sub>

19

A7 🗖 20

A<sub>5</sub> 🖂 18

A<sub>8</sub>

21

$A_9 \square 22$

1/O<sub>2</sub> = 9

# FUNCTIONAL BLOCK DIAGRAM

Document # SRAM133 REV B

44 🗆 A<sub>17</sub>

43 🗖 A<sub>16</sub>

42 A<sub>15</sub> 41 CE

40 BHE

38 1/O<sub>15</sub>

37 1/O<sub>14</sub>

35 🗖 I/O<sub>12</sub>

34 🗖 V<sub>SS</sub>

32 1/011

31 1/O<sub>10</sub>

29 1/O<sub>8</sub>

28 L NC

26 🗆 A<sub>13</sub> 25 🗖 A<sub>12</sub>

36 I/O<sub>13</sub>

33 🗖 Vcc

30 1/O9

27 🗖 A<sub>14</sub>

24 🗖 A<sub>11</sub>

39 🗆 BLE

### Revised September 2008

### RECOMMENDED OPERATING TEMPERATURE AND SUPPLY VOLTAGE

| Grade <sup>(2)</sup> | Ambient Temperature | GND | V <sub>cc</sub> |

|----------------------|---------------------|-----|-----------------|

| Commercial           | 0 - 70°C            | 0V  | 5.0V ± 10%      |

| Industrial           | -40 - 85°C          | 0V  | 5.0V ± 10%      |

| Military             | -55 - 125°C         | 0V  | 5.0V ± 10%      |

### CAPACITANCES (4)

$V_{cc}$  = 5.0V,  $T_{A}$  = 25°C, f = 1.0MHz

| Sym              | Parameter          | Conditions            | Тур. | Unit |

|------------------|--------------------|-----------------------|------|------|

| C                | Input Capacitance  | $V_{IN} = 0V$         | 8    | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = 0V | 8    | pF   |

### MAXIMUM RATINGS (1)

| Sym               | Parameter                               | Value           | Unit |

|-------------------|-----------------------------------------|-----------------|------|

| V <sub>cc</sub>   | Power Supply Pin with<br>Respect to GND | -0.5 to 7.0     | V    |

| V <sub>TERM</sub> | Terminal Voltage with<br>Respect to GND | -0.5 to VCC+0.5 | V    |

| T <sub>A</sub>    | Operating Temperature                   | -55 to 125      | °C   |

| T <sub>BIAS</sub> | Temperature Under Bias                  | -55 to 125      | °C   |

| T <sub>STG</sub>  | Storage Temperature                     | -65 to 150      | °C   |

| I <sub>OUT</sub>  | DC Output Current                       | 20              | mA   |

### **DC ELECTRICAL CHARACTERISTICS**

Over recommended operating temperature and supply voltage  $\ensuremath{^{(2)}}$

| ~                |                                                  |                                                                                                                                                                                                                                  | P40     |                      |      |

|------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------|------|

| Sym              | Sym Parameter                                    | Test Conditions                                                                                                                                                                                                                  | Min     | Мах                  | Unit |

| V <sub>IH</sub>  | Input High Voltage                               |                                                                                                                                                                                                                                  | 2.2     | V <sub>cc</sub> +0.5 | V    |

| V                | Input Low Voltage                                |                                                                                                                                                                                                                                  | -0.5(3) | 0.8                  | V    |

| V <sub>OL</sub>  | Output Low Voltage (TTL Load)                    | $I_{OL}$ = +8 mA, $V_{CC}$ = Min.                                                                                                                                                                                                |         | 0.4                  | V    |

| V <sub>OH</sub>  | Output High Voltage (TTL Load)                   | $I_{OH} = -4 \text{ mA}, V_{CC} = \text{Min}.$                                                                                                                                                                                   | 2.4     |                      | V    |

| I                | Input Leakage Current                            | $V_{cc}$ = Max.<br>$V_{IN}$ = GND to $V_{cc}$                                                                                                                                                                                    | -2      | +2                   | μA   |

| I <sub>lo</sub>  | Output Leakage Current                           | $V_{cc} = Max.,$<br>$\overline{CE} = V_{IH},$<br>$V_{OUT} = GND \text{ to } V_{cc}$                                                                                                                                              | -1      | +1                   | μA   |

| I <sub>SB</sub>  | Standby Power Supply Current (TTL Input Levels)  | $\label{eq:cell} \begin{split} \overline{CE} &\geq V_{_{IH}} \\ V_{_{CC}} &= Max, \\ f &= Max., \ Outputs \ Open \\ V_{_{IN}} &\geq V_{_{IH}} \ or \ V_{_{IN}} &\leq V_{_{IL}} \end{split}$                                      | _       | 40                   | mA   |

| I <sub>SB1</sub> | Standby Power Supply Current (CMOS Input Levels) | $\label{eq:cell} \begin{split} \overline{CE} &\geq V_{cc} \text{-} 0.2 V \\ V_{cc} \text{=} Max, \\ \text{f = 0, Outputs Open} \\ V_{\text{IN}} &\geq V_{cc} \text{-} 0.3 V \text{ or} \\ V_{\text{IN}} &\leq 0.3 V \end{split}$ | _       | 6                    | mA   |

### POWER DISSIPATION CHARACTERISTICS VS. SPEED

| Sym             | Parameter                     | Temperature Range | -10 | -12 | -15 | -20 | Unit |

|-----------------|-------------------------------|-------------------|-----|-----|-----|-----|------|

|                 |                               | Commercial        | 100 | 90  | 80  | 70  | mA   |

| I <sub>cc</sub> | cc Dynamic Operating Current* | Industrial        | 100 | 90  | 80  | 70  | mA   |

|                 |                               | Military          | N/A | 110 | 100 | 90  | mA   |

\*V<sub>cc</sub> = 3.6V. Tested with outputs open. f = Max. Switching inputs are 0V and 3V.  $\overline{CE} = V_{_{IL}}, \overline{OE} = V_{_{IH}}$ .

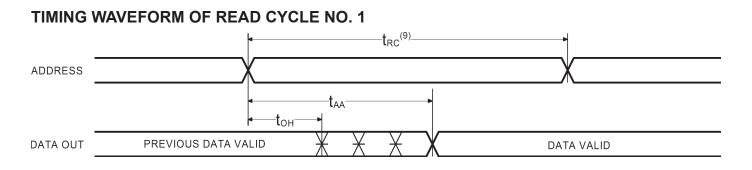

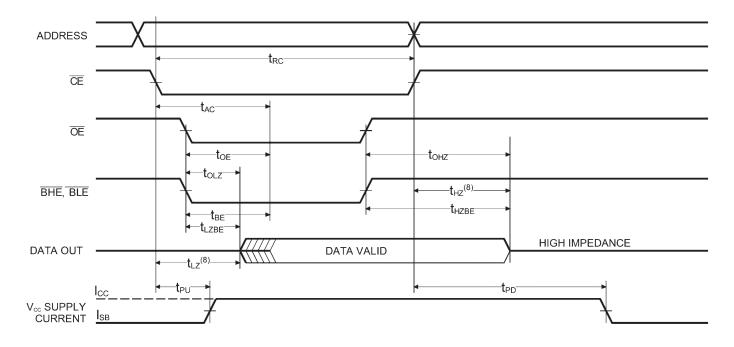

### AC ELECTRICAL CHARACTERISTICS—READ CYCLE

(V<sub>cc</sub> = 5.0V  $\pm$  10%, All Temperature Ranges) <sup>(2)</sup>

| Ci (m             | Baramatar                        | Parameter -10 |     | -12 |     | -15 |     | -20 |     | Unit |

|-------------------|----------------------------------|---------------|-----|-----|-----|-----|-----|-----|-----|------|

| Sym               | ym Parameter                     | Min           | Мах | Min | Max | Min | Мах | Min | Мах | Unit |

| t <sub>RC</sub>   | Read Cycle Time                  | 10            |     | 12  |     | 15  |     | 20  |     | ns   |

| t <sub>AA</sub>   | Address Access Time              |               | 10  |     | 12  |     | 15  |     | 20  | ns   |

| t <sub>AC</sub>   | Chip Enable Access Time          |               | 10  |     | 12  |     | 15  |     | 20  | ns   |

| t <sub>он</sub>   | Output Hold from Address Change  | 3             |     | 3   |     | 3   |     | 3   |     | ns   |

| t <sub>LZ</sub>   | Chip Enable to Output in Low Z   | 3             |     | 3   |     | 3   |     | 3   |     | ns   |

| t <sub>HZ</sub>   | Chip Disable to Output in High Z |               | 5   |     | 6   |     | 7   |     | 8   | ns   |

| t <sub>oe</sub>   | Output Enable Low to Data Valid  |               | 5   |     | 6   |     | 7   |     | 8   | ns   |

| t <sub>olz</sub>  | Output Enable Low to Low Z       | 0             |     | 0   |     | 0   |     | 0   |     | ns   |

| t <sub>oHZ</sub>  | Output Enable High to High Z     |               | 5   |     | 6   |     | 7   |     | 8   | ns   |

| t <sub>PU</sub>   | Chip Enable to Power Up Time     | 0             |     | 0   |     | 0   |     | 0   |     | ns   |

| t <sub>PD</sub>   | Chip Disable to Power Down Time  |               | 10  |     | 12  |     | 15  |     | 20  | ns   |

| t <sub>BE</sub>   | Byte Enable to Data Valid        |               | 5   |     | 6   |     | 7   |     | 8   | ns   |

| t <sub>LZBE</sub> | Byte Enable to Low Z             | 0             |     | 0   |     | 0   |     | 0   |     | ns   |

| t <sub>HZBE</sub> | Byte Disable to High Z           |               | 6   |     | 6   |     | 7   |     | 8   | ns   |

### TIMING WAVEFORM OF READ CYCLE NO. 2 (OE CONTROLLED)<sup>(5,6)</sup>

### Notes:

- Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to MAXIMUM rating conditions for extended periods may affect reliability.

- 2. Extended temperature operation guaranteed with 400 linear feet per minute of air flow.

- 3. Transient inputs with  $V_{_{\rm I\!L}}$  not more negative than –2.0V and

$V_{IH} \le V_{CC}$  + 0.5V, are permissible for pulse widths up to 20 ns.

- 4. This parameter is sampled and not 100% tested.

- 5. WE is HIGH for READ cycle.

- 6.  $\overline{CE}$  is LOW and  $\overline{OE}$  is LOW for READ cycle.

- 7. ADDRESS must be valid prior to, or coincident with CE transition LOW.

- Transition is measured ± 200 mV from steady state voltage prior to change, with loading as specified in Figure 1. This parameter is sampled and not 100% tested.

- 9. Read Cycle Time is measured from the last valid address to the first transitioning address.

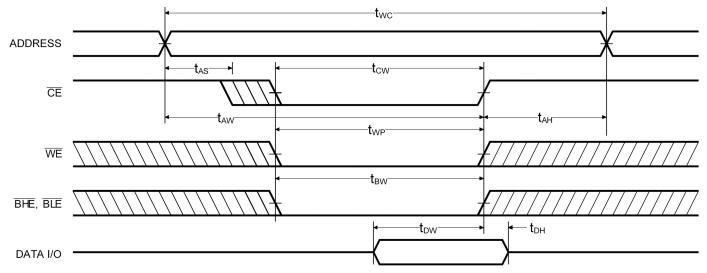

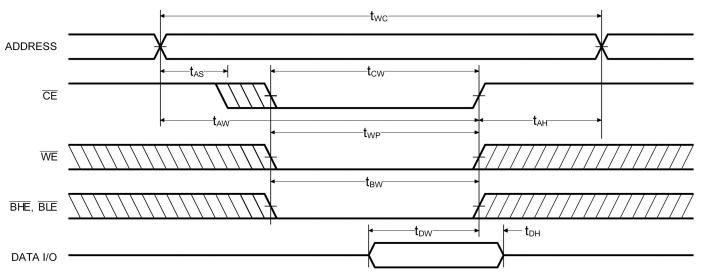

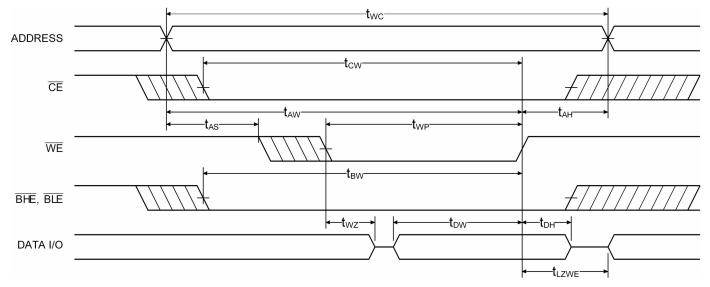

### AC CHARACTERISTICS—WRITE CYCLE

$(V_{cc} = 5.0V \pm 10\%, All \text{ Temperature Ranges})^{(2)}$

| Crime             | Sum Baramatan                     |     | 10  | -12 |     | -15 |     | -20 |     | Unit |

|-------------------|-----------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| Sym.              | Parameter                         | Min | Мах | Min | Max | Min | Мах | Min | Мах |      |

| t <sub>wc</sub>   | Write Cycle Time                  | 10  |     | 12  |     | 15  |     | 20  |     | ns   |

| t <sub>cw</sub>   | Chip Enable Time To End Of Write  | 7   |     | 8   |     | 10  |     | 10  |     | ns   |

| t <sub>AW</sub>   | Address Valid To End Of Write     | 7   |     | 8   |     | 10  |     | 10  |     | ns   |

| t <sub>AS</sub>   | Address Setup Time To Write Start | 0   |     | 0   |     | 0   |     | 0   |     | ns   |

| t <sub>wP</sub>   | Write Pulse Width                 | 7   |     | 8   |     | 10  |     | 10  |     | ns   |

| t <sub>AH</sub>   | Address Hold Time                 | 0   |     | 0   |     | 0   |     | 0   |     | ns   |

| t <sub>DW</sub>   | Data Valid To End Of Write        | 5   |     | 6   |     | 7   |     | 8   |     | ns   |

| t <sub>DH</sub>   | Data Hold Time                    | 0   |     | 0   |     | 0   |     | 0   |     | ns   |

| t <sub>wz</sub>   | Write Enable To Output In High Z  |     | 5   |     | 6   |     | 7   |     | 8   | ns   |

| t <sub>ow</sub>   | Output Active From End Of Write   | 5   |     | 5   |     | 0   |     | 0   |     | ns   |

| t <sub>LZWE</sub> | WE High To Low Z                  | 3   |     | 3   |     | 3   |     | 3   |     | ns   |

| t <sub>BW</sub>   | Byte Enable To End Of Write       | 7   |     | 8   |     | 10  |     | 10  |     | ns   |

### TIMING WAVEFORM OF WRITE CYCLE NO. 1 (CE CONTROLLED)

# TIMING WAVEFORM OF WRITE CYCLE NO. 2 (BLE OR BHE CONTROLLED)

TIMING WAVEFORM OF WRITE CYCLE NO. 3 ( $\overline{\text{WE}}$  CONTROLLED,  $\overline{\text{OE}}$  LOW)

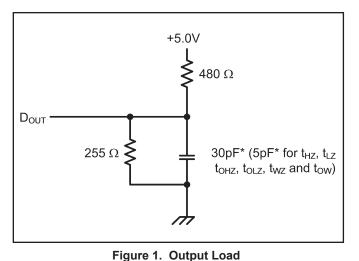

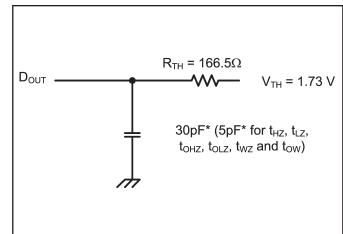

### AC TEST CONDITIONS

| Input Pulse Levels            | GND to 3.0V       |

|-------------------------------|-------------------|

| Input Rise and Fall Times     | 3ns               |

| Input Timing Reference Level  | 1.5V              |

| Output Timing Reference Value | 1.5V              |

| Output Load                   | See Figures 1 & 2 |

Figure 2. Thevenin Equivalent

\* including scope and test fixture.

### Note:

Because of the ultra-high speed of the P4C1041, care must be taken when testing this device; an inadequate setup can cause a normal functioning part to be rejected as faulty. Long high-inductance leads that cause supply bounce must be avoided by bringing the V<sub>cc</sub> and ground planes directly up to the contactor fingers. A 0.01 µF high frequency capacitor is also required between V<sub>cc</sub> and ground. To avoid signal reflections,

proper termination must be used; for example, a 50 $\Omega$  test environment should be terminated into a 50 $\Omega$  load with 1.73V (Thevenin Voltage) at the comparator input, and a 116 $\Omega$  resistor must be used in series with D<sub>out</sub> to match 166 $\Omega$  (Thevenin Resistance).

### **TRUTH TABLE**

| Mode                       | CE | ŌĒ | WE | BLE | BHE | I/O <sub>0</sub> - I/O <sub>7</sub> | 1/O <sub>8</sub> - 1/O <sub>15</sub> | Power   |

|----------------------------|----|----|----|-----|-----|-------------------------------------|--------------------------------------|---------|

| Powerdown                  | н  | X  | X  | X   | X   | High Z                              | High Z                               | Standby |

| Read All Bits              | L  | L  | Н  | L   | L   | D <sub>OUT</sub>                    | D <sub>OUT</sub>                     | Active  |

| Read Lower Bits Only       | L  | L  | Н  | L   | н   | D <sub>OUT</sub>                    | High Z                               | Active  |

| Read Upper Bits Only       | L  | L  | Н  | Н   | L   | High Z                              | D <sub>OUT</sub>                     | Active  |

| Write All Bits             | L  | Х  | L  | L   | L   | D <sub>IN</sub>                     | D <sub>IN</sub>                      | Active  |

| Write Lower Bits Only      | L  | Х  | L  | L   | н   | D <sub>IN</sub>                     | High Z                               | Active  |

| Write Upper Bits Only      | L  | Х  | L  | н   | L   | High Z                              | D <sub>IN</sub>                      | Active  |

| Selected, Outputs Disabled | L  | Н  | Н  | Х   | Х   | High Z                              | High Z                               | Active  |

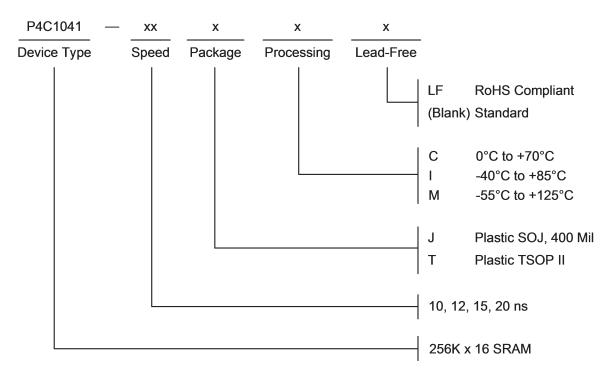

### **ORDERING INFORMATION**

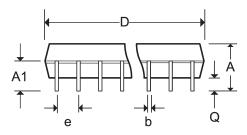

| Pkg #  | J8     |         |  |  |

|--------|--------|---------|--|--|

| # Pins | 44 (40 | 00 mil) |  |  |

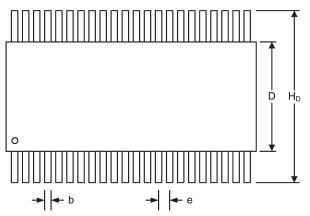

| Symbol | Min    | Max     |  |  |

| А      | 0.128  | 0.148   |  |  |

| A1     | 0.082  | -       |  |  |

| b      | 0.013  | 0.023   |  |  |

| С      | 0.007  | 0.013   |  |  |

| D      | 1.120  | 1.130   |  |  |

| е      | 0.050  | BSC     |  |  |

| Е      | 0.435  | 0.445   |  |  |

| E1     | 0.395  | 0.405   |  |  |

| E2     | 0.370  | BSC     |  |  |

| Q      | 0.025  | -       |  |  |

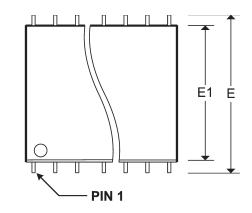

### SOJ SMALL OUTLINE IC PACKAGE

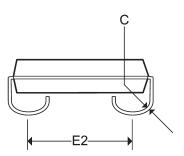

| Pkg #          | Т2         |       |  |  |  |  |

|----------------|------------|-------|--|--|--|--|

| # Pins         | 44         |       |  |  |  |  |

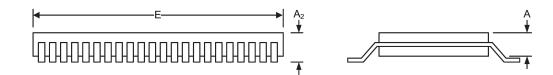

| Symbol         | Min        | Max   |  |  |  |  |

| А              | 0.039      | 0.047 |  |  |  |  |

| A <sub>2</sub> | 0.033      | 0.045 |  |  |  |  |

| b              | 0.012      | 0.016 |  |  |  |  |

| D              | 0.396      | 0.404 |  |  |  |  |

| E              | 0.721      | 0.729 |  |  |  |  |

| е              | 0.0315 BSC |       |  |  |  |  |

| H <sub>D</sub> | 0.462      | 0.470 |  |  |  |  |

## TSOP II THIN SMALL OUTLINE PACKAGE

### REVISIONS

| DOCUMENT NUMBER | SRAM 133                                             |

|-----------------|------------------------------------------------------|

| DOCUMENT TITLE  | P4C1041 HIGH SPEED 256K X 16 (4 MEG) STATIC CMOS RAM |

| JDB<br>JDB<br>JDB | New Data Sheet         Added Military processing, lead-free designation         Updated TSOP II Package Drawing |

|-------------------|-----------------------------------------------------------------------------------------------------------------|

|                   |                                                                                                                 |

| JDB               | Updated TSOP II Package Drawing                                                                                 |

|                   |                                                                                                                 |

|                   |                                                                                                                 |

|                   |                                                                                                                 |

|                   |                                                                                                                 |

|                   |                                                                                                                 |

|                   |                                                                                                                 |

|                   |                                                                                                                 |

|                   |                                                                                                                 |

|                   |                                                                                                                 |

|                   |                                                                                                                 |

|                   |                                                                                                                 |

|                   |                                                                                                                 |

|                   |                                                                                                                 |

|                   |                                                                                                                 |

|                   |                                                                                                                 |

|                   |                                                                                                                 |

|                   |                                                                                                                 |

|                   |                                                                                                                 |