# HIGH SPEED 256 X 4 STATIC CMOS RAM

#### **FEATURES**

- High Speed (Equal Access and Cycle Times)

- 10/12/15/20/25/35 ns (Commercial)

- 15/20/25/35 ns (Military)

- CMOS for Low Power

- 495 mW Max. 10/12/15/20/25 (Commercial)

- 495 mW Max. 15/20/25/35 (Military)

- Single 5V±10% Power Supply

- Separate I/O

- **■** Fully TTL Compatible Inputs and Outputs

- Resistant to single event upset and latchup resulting from advanced process and design improvements.

- Standard Pinout (JEDEC Approved)

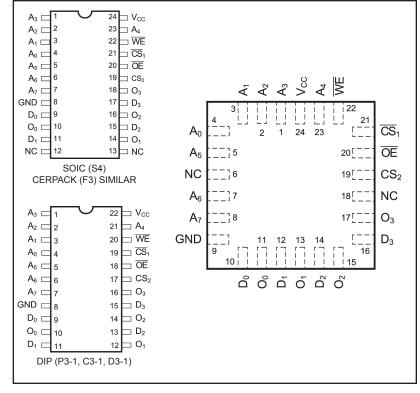

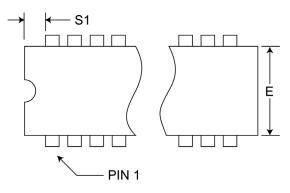

- 22-Pin 400 mil DIP

- 24-Pin 300 mil SOIC

- 24-Pin Square LCC

- 24-Pin CERPACK

#### **DESCRIPTION**

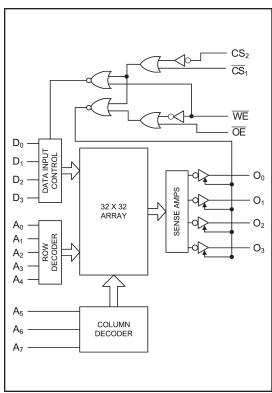

The P4C422 is a 1,024-bit high-speed (10ns) Static RAM with a 256 x 4 organization. The memory requires no clocks or refreshing and has equal access and cycle times. Inputs and outputs are fully TTL compatible. Operation is from a single 5 Volt supply. Easy memory expansion is provided by an active LOW chip select one  $(\overline{CS}_1)$  and active HIGH chip select two  $(CS_2)$  as well as 3-state outputs.

In addition to high performance and high density, the device features latch-up protection, single event and upset protection. The P4C422 is offered in several packages: 22-pin 400 mil DIP (plastic and ceramic), 24-pin 300 mil SOIC, 24-pin square LCC and 24-pin CERPACK. Devices are offered in both commercial and military temperature ranges.

#### **FUNCTIONAL BLOCK DIAGRAM**

#### PIN CONFIGURATIONS

#### MAXIMUM RATINGS(1)

| Sym               | Parameter                                               | Value             | Unit |

|-------------------|---------------------------------------------------------|-------------------|------|

| V <sub>cc</sub>   | Power Supply Pin with Respect to GND                    | -0.5 to +7        | V    |

| V <sub>TERM</sub> | Terminal Voltage with<br>Respect to GND (up to<br>7.0V) | -0.5 to VCC + 0.5 | V    |

| T <sub>A</sub>    | Operating Temperature                                   | -55 to +125       | °C   |

| T <sub>BIAS</sub> | Temperature Under Bias                                  | -55 to +125       | °C   |

| T <sub>STG</sub>  | Storage Temperature                                     | -65 to +150       | °C   |

| I <sub>out</sub>  | DC Output Current                                       | 50                | mA   |

## RECOMMENDED OPERATING CONDITIONS

| Grade <sup>(2)</sup> | Ambient Temp    | GND | V <sub>cc</sub> |

|----------------------|-----------------|-----|-----------------|

| Commercial           | 0°C to 70°C     | 0V  | 5.0V ± 10%      |

| Military             | -55°C to +125°C | 0V  | 5.0V ± 10%      |

## CAPACITANCES(4)

$(V_{CC} = 5.0V, T_A = 25^{\circ}C, f = 1.0MHz)$

| Sym              | Parameter          | Conditions           | Тур | Unit |

|------------------|--------------------|----------------------|-----|------|

| C <sub>IN</sub>  | Input Capacitance  | V <sub>IN</sub> =0V  | 5   | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>out</sub> =0V | 7   | pF   |

#### DC ELECTRICAL CHARACTERISTICS

(Over Recommended Operating Temperature & Supply Voltage)(2)

| 0               | Bananatan                       | Test Conditions                                     | P40  | P4C422 |      |  |  |

|-----------------|---------------------------------|-----------------------------------------------------|------|--------|------|--|--|

| Sym             | Parameter                       | arameter rest conditions                            | Min  | Max    | Unit |  |  |

| V <sub>OH</sub> | Output High Voltage             | I <sub>OH</sub> = -5.2 mA, V <sub>CC</sub> =Min 2.4 | 2.4  |        | V    |  |  |

| V <sub>OL</sub> | Output Low Voltage              | I <sub>oL</sub> = +8 mA, V <sub>cc</sub> =Min       |      | 0.4    | V    |  |  |

| V <sub>IH</sub> | Input High Voltage              |                                                     | 2.1  |        | V    |  |  |

| V <sub>IL</sub> | Input Low Voltage               |                                                     |      | 0.8    | V    |  |  |

| V <sub>CL</sub> | Input Clamp Diode Voltage       | I <sub>IN</sub> = -10 mA                            | -1.5 |        | V    |  |  |

| I <sub>IX</sub> | Input Load Current              | GND ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>             | -10  | 10     | μΑ   |  |  |

| l <sub>oz</sub> | Output Current (High Z)         | $V_{OL} \le V_{OUT} \le V_{OH}$ , Output Disabled   | -10  | 10     | μA   |  |  |

| I <sub>os</sub> | Output Short Circuit Current(3) | V <sub>cc</sub> =Max, V <sub>out</sub> =GND         |      | 90     | mA   |  |  |

#### POWER DISSIPATION CHARACTERISTICS VS. SPEED

| Sym | Parameter                 | Temperature Range | -10 | -12 | -15 | -20 | -25 | -35 | Unit |

|-----|---------------------------|-------------------|-----|-----|-----|-----|-----|-----|------|

|     | Dynamia Operating Current | Commercial        | 90  | 90  | 90  | 90  | 65  | 65  | mA   |

| cc  | Dynamic Operating Current | Military          | N/A | N/A | 90  | 90  | 90  | 90  | mA   |

#### Notes:

- Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to MAXIMUM rating conditions for extended periods may affect reliability.

- 2. Extended temperature operation guaranteed with 400 linear feet per minute of air flow.

- For test purposes, not more than one output at a time should be shorted. Short circuit test duration should not exceed 30 seconds.

- 4. This parameter is sampled and not 100% tested.

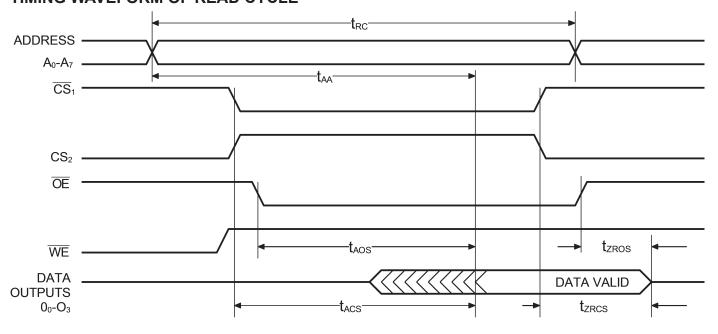

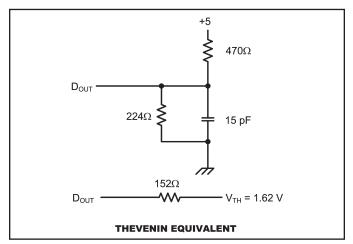

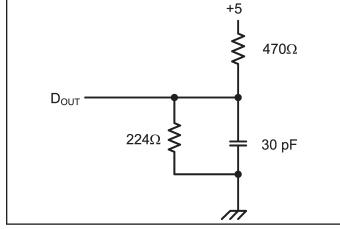

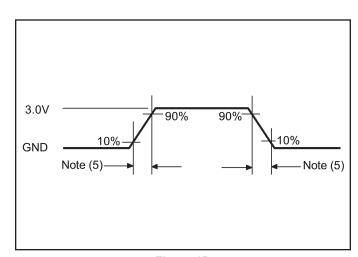

- 5. Transition time is ≤ 3ns for 10,12, and 15 ns products and ≤ 5ns for 20, 25, and 35 ns products, see Fig 1d. Timing is referenced at input and output levels of 1.5V. The output loading is equivalent to the specified I<sub>OL</sub>/I<sub>OH</sub> with a load capacitance of 15 pF (10,12) or 30 pF (15, 20, 25, 35) as in Fig.1a and 1b respectively.

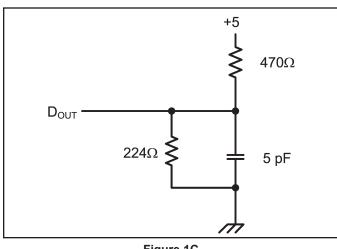

- 6. Transition time is ≤ 3ns for 10, 12, and 15ns products and ≤ 5ns for 20, 25, and 35ns products, see Fig 1d. Transition is measured at steady state HIGH level -500mV or steady state LOW level +500mV on the output from a level on the input with load shown in Fig. 1c.

- 7.  $t_{\rm w}$  is measured at  $t_{\rm wsa}$ =min.;  $t_{\rm wsa}$  is measured at  $t_{\rm w}$ =min.

#### FUNCTIONAL DESCRIPTION

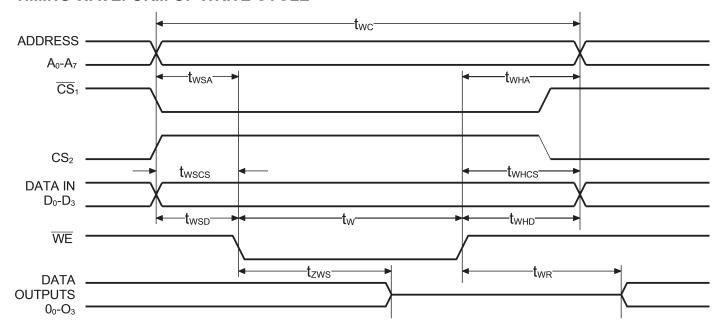

An active LOW write enable  $(\overline{WE})$  controls the writing/reading operation of the memory. When the chip select one  $(\overline{CS}_1)$  and the write enable  $(\overline{WE})$  are LOW and the chip select two  $(CS_2)$  is HIGH, the information on data inputs  $(D_0)$  through  $D_3$  is written into the addressed memory word and preconditions the output circuitry so that true data is present at the outputs when the write cycle is complete. This preconditioning operation insures minimum write recovery

times by eliminating the "write recovery glitch." Reading is performed with chip select one  $(\overline{CS}_1)$  LOW, chip select two  $(CS_2)$  HIGH, write enable  $(\overline{WE})$  HIGH and output enable  $(\overline{OE})$  LOW. The information stored in the addressed word is read out on the noninverting outputs  $(O_0$  through  $O_3$ ). The outputs of the memory go to an inactive high impedance state whenever chip select one  $(\overline{CS}_1)$  is HIGH, or during the write operation when write enable  $(\overline{WE})$  is LOW.

#### TRUTH TABLE

| Mode                      | CS <sub>2</sub> | \overline{CS}_1 | WE | ŌĒ | Output           |

|---------------------------|-----------------|-----------------|----|----|------------------|

| Standby                   | L               | Х               | Х  | Х  | High Z           |

| Standby                   | Х               | Н               | Х  | Х  | High Z           |

| D <sub>OUT</sub> Disabled | Н               | L               | Х  | Н  | High Z           |

| Read                      | Н               | L               | Н  | L  | D <sub>out</sub> |

| Write                     | Н               | L               | L  | Х  | High Z           |

#### Notes:

H = HIGH L = LOW X = Don't Care

HIGH Z = Implies outputs are disabled or off. This condition is defined as high impedance state for the P4C422.

## AC ELECTRICAL CHARACTERISTICS—READ CYCLE

$(V_{CC} = 5V \pm 10\% \text{ except as noted, All Temperature Ranges})^{(2)}$

| Sum               | Parameter                   | -1  | 0*  | -1  | 12  | -1  | 15  | -2  | 20  | -2  | 25  | -3  | 35  | Unit  |

|-------------------|-----------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| Sym               | Parameter                   | Min | Max | Offic |

| t <sub>RC</sub>   | Read Cycle Time (5)         | 12  |     | 12  |     | 15  |     | 20  |     | 25  |     | 35  |     | ns    |

| t <sub>ACS</sub>  | Chip Select Time (5)        |     | 7.5 |     | 8   |     | 8   |     | 12  |     | 15  |     | 25  | ns    |

| t <sub>zrcs</sub> | Chip Select to High-Z (6)   |     | 8   |     | 10  |     | 12  |     | 15  |     | 20  |     | 30  | ns    |

| t <sub>AOS</sub>  | Output Enable Time          |     | 7.5 |     | 8   |     | 8   |     | 12  |     | 15  |     | 25  | ns    |

| t <sub>zros</sub> | Output Enable to High-Z (6) |     | 8   |     | 10  |     | 12  |     | 15  |     | 20  | ·   | 30  | ns    |

| t <sub>AA</sub>   | Address Access Time (5)     |     | 10  |     | 12  |     | 15  |     | 20  |     | 25  |     | 35  | ns    |

$V_{CC} = 5V \pm 5\%$

### TIMING WAVEFORM OF READ CYCLE

## AC CHARACTERISTICS—WRITE CYCLE

$(V_{CC} = 5V \pm 10\%, All Temperature Ranges)^{(2)}$

| Cum               | Parameter                             | -1  | 0*  | -1  | 2   | -1  | 15  | -2  | 20  | -2  | 25  | -3  | 35  | l loit |

|-------------------|---------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|--------|

| Sym               | raiailietei                           | Min | Max | Unit   |

| t <sub>wc</sub>   | Write Cycle Time <sup>(5)</sup>       | 10  |     | 12  |     | 15  |     | 20  |     | 25  |     | 35  |     | ns     |

| t <sub>zws</sub>  | Write Enable to High-Z <sup>(6)</sup> |     | 8   |     | 10  |     | 12  |     | 15  |     | 20  |     | 30  | ns     |

| t <sub>wR</sub>   | Write Recovery Time                   |     | 8   |     | 10  |     | 12  |     | 15  |     | 20  |     | 25  | ns     |

| t <sub>w</sub>    | Write Pulse Width(5,7)                | 8   |     | 9   |     | 11  |     | 13  |     | 15  |     | 20  |     | ns     |

| t <sub>wsp</sub>  | Data Setup Time Prior to Write(5)     | 0   |     | 0   |     | 0   |     | 2   |     | 5   |     | 5   |     | ns     |

| t <sub>whd</sub>  | Data Hold Time <sup>(5)</sup>         | 2   |     | 2   |     | 2   |     | 5   |     | 5   |     | 5   |     | ns     |

| t <sub>wsa</sub>  | Address Setup Time(5)                 | 0   |     | 0   |     | 0   |     | 2   |     | 5   |     | 5   |     | ns     |

| t <sub>wha</sub>  | Address Hold Time <sup>(5)</sup>      | 2   |     | 2   |     | 4   |     | 5   |     | 5   |     | 5   |     | ns     |

| t <sub>wscs</sub> | Chip Select Setup Time <sup>(5)</sup> | 0   |     | 0   |     | 0   |     | 2   |     | 5   |     | 5   |     | ns     |

| t <sub>whcs</sub> | Chip Select Hold Time(5)              | 2   |     | 2   |     | 2   |     | 5   |     | 5   |     | 5   |     | ns     |

## TIMING WAVEFORM OF WRITE CYCLE

<sup>10.</sup>  $\overline{\text{CE}}$  and  $\overline{\text{WE}}$  must be LOW for WRITE cycle.

<sup>11.</sup> OE is LOW for this WRITE cycle to show t<sub>wz</sub> and t<sub>ow</sub>.

12. If CE goes HIGH simultaneously with WE HIGH, the output remains in a high impedance state

<sup>13.</sup> Write Cycle Time is measured from the last valid address to the first transitioning address.

## **AC TEST LOADS & WAVEFORMS**

Figure 1A

Figure 1B

Figure 1C

Figure 1D

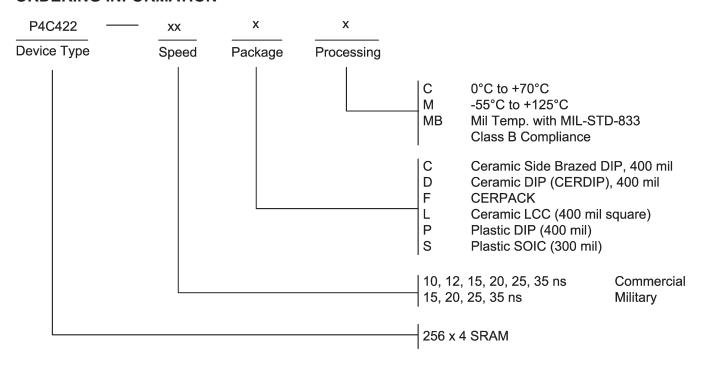

## **ORDERING INFORMATION**

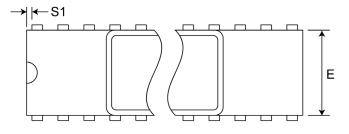

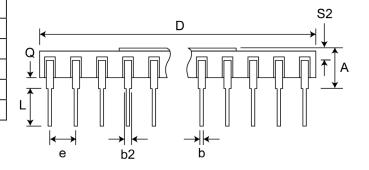

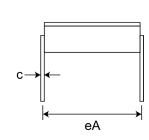

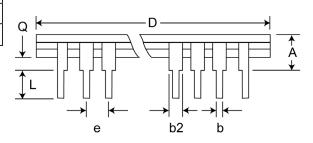

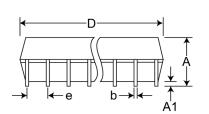

| •      |              |       |  |  |  |

|--------|--------------|-------|--|--|--|

| Pkg#   | C3-1         |       |  |  |  |

| # Pins | 22 (400 Mil) |       |  |  |  |

| Symbol | Min          | Max   |  |  |  |

| А      | -            | 0.200 |  |  |  |

| b      | 0.014        | 0.026 |  |  |  |

| b2     | 0.035        | 0.060 |  |  |  |

| С      | 0.008        | 0.015 |  |  |  |

| D      | -            | 1.100 |  |  |  |

| Е      | 0.360        | 0.410 |  |  |  |

| eA     | 0.400        | BSC   |  |  |  |

| е      | 0.100        | BSC   |  |  |  |

| L      | 0.125        | 0.200 |  |  |  |

| Q      | 0.015        | 0.060 |  |  |  |

| S1     | 0.005        | -     |  |  |  |

| S2     | 0.005        | -     |  |  |  |

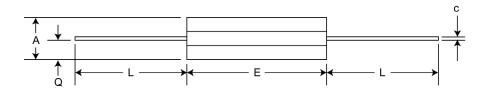

## SIDEBRAZED DUAL IN-LINE PACKAGE

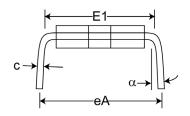

| Pkg #  | D3-1         |       |  |  |  |

|--------|--------------|-------|--|--|--|

| # Pins | 22 (400 Mil) |       |  |  |  |

| Symbol | Min          | Max   |  |  |  |

| Α      | -            | 0.225 |  |  |  |

| b      | 0.014        | 0.026 |  |  |  |

| b2     | 0.045        | 0.065 |  |  |  |

| С      | 0.008        | 0.018 |  |  |  |

| D      | -            | 1.111 |  |  |  |

| Е      | 0.350        | 0.410 |  |  |  |

| eA     | 0.400        | BSC   |  |  |  |

| е      | 0.100        | BSC   |  |  |  |

| L      | 0.125        | 0.200 |  |  |  |

| Q      | 0.015        | 0.070 |  |  |  |

| S1     | 0.005        | -     |  |  |  |

| α      | 0°           | 15°   |  |  |  |

## **CERDIP DUAL IN-LINE PACKAGE**

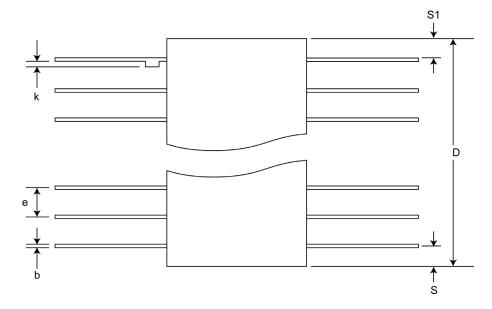

| •      |       |       |  |  |  |  |

|--------|-------|-------|--|--|--|--|

| Pkg #  | F3    |       |  |  |  |  |

| # Pins | 24    |       |  |  |  |  |

| Symbol | Min   | Max   |  |  |  |  |

| А      | 0.060 | 0.090 |  |  |  |  |

| b      | 0.015 | 0.022 |  |  |  |  |

| С      | 0.004 | 0.009 |  |  |  |  |

| D      | -     | 0.630 |  |  |  |  |

| Е      | 0.330 | 0.380 |  |  |  |  |

| е      | 0.050 | BSC   |  |  |  |  |

| k      | 0.008 | 0.015 |  |  |  |  |

| L      | 0.250 | 0.370 |  |  |  |  |

| Q      | 0.026 | 0.045 |  |  |  |  |

| S      | -     | 0.085 |  |  |  |  |

| S1     | 0.005 | -     |  |  |  |  |

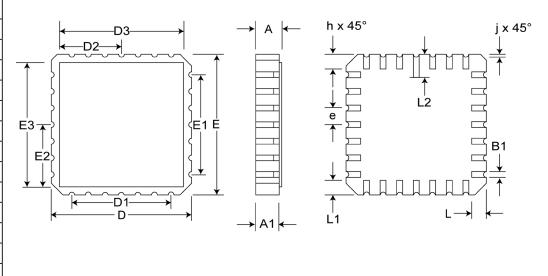

## **CERPACK CERAMIC FLAT PACKAGE**

| Pkg#   | L4          |       |  |  |  |

|--------|-------------|-------|--|--|--|

| # Pins | 2           | 4     |  |  |  |

| Symbol | Min         | Max   |  |  |  |

| Α      | 0.060       | 0.075 |  |  |  |

| A1     | 0.050       | 0.065 |  |  |  |

| B1     | 0.022       | 0.028 |  |  |  |

| D/E    | 0.395       | 0.410 |  |  |  |

| D1/E1  | 0.250 BSC   |       |  |  |  |

| D2/E2  | 0.125 BSC   |       |  |  |  |

| D3/E3  | ı           | 0.410 |  |  |  |

| е      | 0.050       | BSC   |  |  |  |

| h      | 0.040       | REF   |  |  |  |

| j      | 0.020       | REF   |  |  |  |

| L      | 0.045       | 0.055 |  |  |  |

| L1     | 0.045       | 0.055 |  |  |  |

| L2     | 0.075 0.095 |       |  |  |  |

| ND     | 6           |       |  |  |  |

| NE     | 6           |       |  |  |  |

# **SQUARE LEADLESS CHIP CARRIER**

| ~      |              |       |  |

|--------|--------------|-------|--|

| Pkg#   | P3-1         |       |  |

| # Pins | 22 (400 Mil) |       |  |

| Symbol | Min          | Max   |  |

| Α      | -            | 0.210 |  |

| A1     | 0.015        | -     |  |

| b      | 0.014        | 0.022 |  |

| b2     | 0.045        | 0.065 |  |

| С      | 0.009        | 0.015 |  |

| D      | 1.065        | 1.120 |  |

| E1     | 0.330        | 0.390 |  |

| Е      | 0.390        | 0.425 |  |

| е      | 0.100 BSC    |       |  |

| eВ     | -            | 0.500 |  |

| L      | 0.115        | 0.160 |  |

| α      | 0°           | 15°   |  |

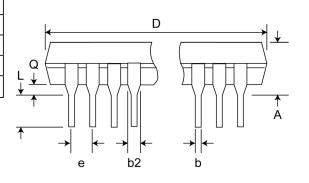

## PLASTIC DUAL IN-LINE PACKAGE

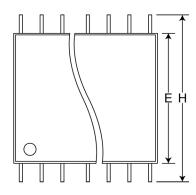

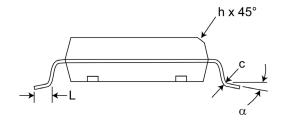

| Pkg#   | S4           |       |

|--------|--------------|-------|

| # Pins | 24 (300 Mil) |       |

| Symbol | Min          | Max   |

| Α      | 0.093        | 0.104 |

| A1     | 0.004        | 0.012 |

| b2     | 0.013        | 0.020 |

| С      | 0.009        | 0.012 |

| D      | 0.598        | 0.614 |

| е      | 0.050 BSC    |       |

| Е      | 0.291        | 0.299 |

| Н      | 0.394        | 0.419 |

| h      | 0.010        | 0.029 |

| L      | 0.016        | 0.050 |

| α      | 0°           | 8°    |

# **SMALL OUTLINE IC PLASTIC PACKAGE**

# **REVISIONS**

| DOCUMENT NUMBER | SRAM 101                                    |  |

|-----------------|---------------------------------------------|--|

| DOCUMENT TITLE  | P4C422 - HIGH SPEED 256 X 4 STATIC CMOS RAM |  |

| REV | ISSUE DATE | ORIGINATOR | DESCRIPTION OF CHANGE                         |

|-----|------------|------------|-----------------------------------------------|

| OR  | 1997       | DAB        | New Data Sheet                                |

| Α   | Oct-2005   | JDB        | Changed logo to Pyramid                       |

| В   | Aug-2009   | JDB        | Corrected DC Electrical Characteristics table |

Document #SRAm101 REV B