2K X 8 EEPROM

#### **FEATURES**

- Access Times of 150, 200, 250 and 350ns

- Single 5V±10% Power Supply

- Fast Byte Write (200µs or 1 ms)

- Low Power CMOS:

- 60 mA Active Current

- 150 µA Standby Current

- Fast Write Cycle Time DATA Polling

- CMOS & TTL Compatible Inputs and Outputs

- Endurance:

- 10,000 Write Cycles

- 100,000 Write Cycles (optional)

- Data Retention: 10 Years

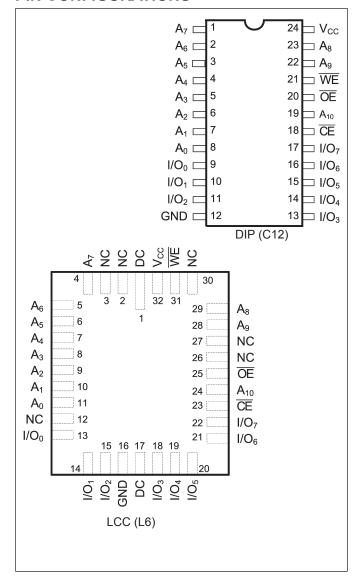

- Available in the following package:

- 24-Pin 600 mil Ceramic DIP

- 32-Pin Ceramic LCC (450x550 mils)

## **1**

#### **DESCRIPTION**

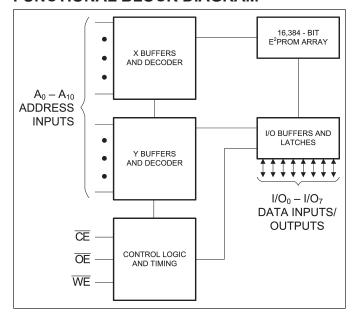

The PYA28C16 is a 5 Volt 2Kx8 EEPROM. The PYA28C16 is a 16K memory organized as 2,048 words by 8 bits. Data Retention is 10 Years. The device is available in a 24-Pin 600 mil wide Ceramic DIP and 32-Pin LCC.

# **•**

#### FUNCTIONAL BLOCK DIAGRAM

#### PIN CONFIGURATIONS

#### **OPERATION**

#### **READ**

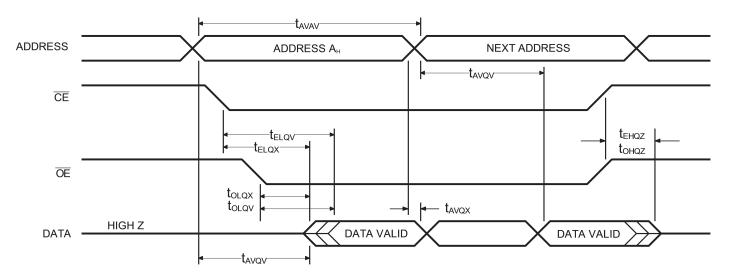

Read operations are initiated by both  $\overline{OE}$  and  $\overline{CE}$  LOW. The read operation is terminated by either  $\overline{CE}$  or  $\overline{OE}$  returning HIGH. This two line control architecture eliminates bus contention in a system environment. The data bus will be in a high impedance state when either  $\overline{OE}$  or  $\overline{CE}$  is HIGH.

#### **BYTE WRITE**

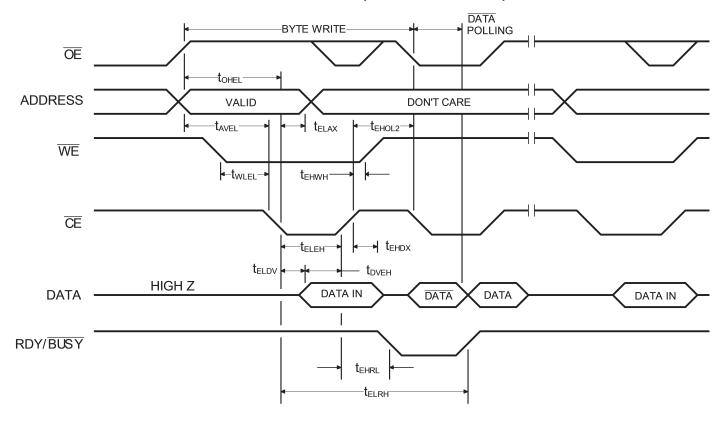

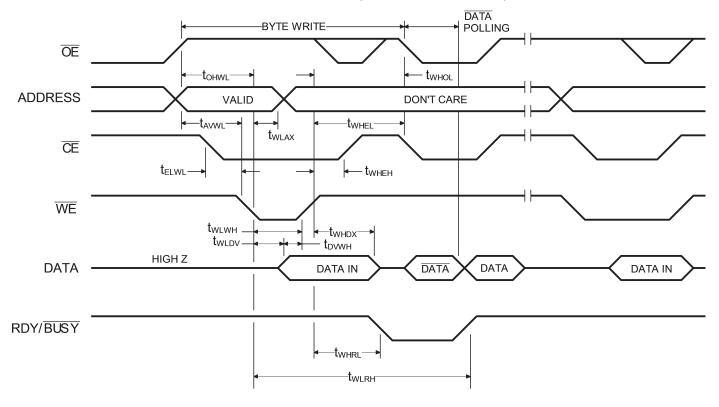

Write operations are initiated when both  $\overline{\text{CE}}$  and  $\overline{\text{WE}}$  are LOW and  $\overline{\text{OE}}$  is HIGH. The PYA28C16 supports both a  $\overline{\text{CE}}$  and  $\overline{\text{WE}}$  controlled write cycle. That is, the address is latched by the falling edge of either  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ , whichever occurs last. Similarly, the data is latched internally by the rising edge of either  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ , whichever occurs first. A byte write operation, once initiated, will automatically continue to completion.

#### **CHIP CLEAR**

The contents of the entire memory of the PYA28C16 may be set to the high state by the CHIP CLEAR operation. By setting  $\overline{\text{CE}}$  low and  $\overline{\text{OE}}$  to 12 volts, the chip is cleared when a 10 msec low pulse is applied to  $\overline{\text{WE}}$ .

#### **DEVICE IDENTIFICATION**

An extra 32 bytes of EEPROM memory are available to the user for device identification. By raising A $_{\rm g}$  to 12  $\pm$  0.5V and using address locations 7E0H to 7FFH the additional bytes may be written to or read from in the same manner as the regular memory array.

#### DATA POLLING

The PYA28C16 features  $\overline{\text{DATA}}$  Polling as a method to indicate to the host system that the byte write cycle has completed.  $\overline{\text{DATA}}$  Polling allows a simple bit test operation to determine the status of the PYA28C16, eliminating additional interrupts or external hardware. During the internal programming cycle, any attempt to read the last byte written will produce the complement of that data on I/O<sub>7</sub> (i.e., write data=0xxx xxxx, read data=1xxx xxxx). Once the programming cycle is complete, I/O<sub>7</sub> will reflect true data.

#### MAXIMUM RATINGS(1)

| Sym               | Parameter                                                | Value         | Unit |

|-------------------|----------------------------------------------------------|---------------|------|

| V <sub>cc</sub>   | Power Supply Pin with Respect to GND                     | -0.3 to +6.25 | V    |

| V <sub>TERM</sub> | Terminal Voltage with<br>Respect to GND (up to<br>6.25V) | -0.5 to +6.25 | V    |

| T <sub>A</sub>    | Operating Temperature                                    | -55 to +125   | °C   |

| T <sub>BIAS</sub> | Temperature Under Bias                                   | -55 to +125   | °C   |

| T <sub>STG</sub>  | Storage Temperature                                      | -65 to +150   | °C   |

| P <sub>T</sub>    | Power Dissipation                                        | 1.0           | W    |

| I <sub>out</sub>  | DC Output Current                                        | 50            | mA   |

#### RECOMMENDED OPERATING CONDITIONS

| Grade <sup>(2)</sup> | Ambient Temp    | GND | V <sub>cc</sub> |

|----------------------|-----------------|-----|-----------------|

| Military             | -55°C to +125°C | 0V  | 5.0V ± 10%      |

#### CAPACITANCES(4)

$(V_{CC} = 5.0V, T_{A} = 25^{\circ}C, f = 1.0MHz)$

| Sym              | Parameter          | Conditions            | Тур | Unit |

|------------------|--------------------|-----------------------|-----|------|

| C <sub>IN</sub>  | Input Capacitance  | V <sub>IN</sub> = 0V  | 10  | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = 0V | 10  | pF   |

#### DC ELECTRICAL CHARACTERISTICS

(Over Recommended Operating Temperature & Supply Voltage)(2)

|                  | Barrandari                                       | T - 1 0 - 1 11                                                                                                                                                                                                                | PYA28C16              |                       | 11:4 |

|------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|------|

| Sym              | Parameter                                        | Test Conditions                                                                                                                                                                                                               | Min                   | Max                   | Unit |

| V <sub>IH</sub>  | Input High Voltage                               |                                                                                                                                                                                                                               | 2.0                   | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IL</sub>  | Input Low Voltage                                |                                                                                                                                                                                                                               | -0.5(3)               | 0.8                   | V    |

| V <sub>HC</sub>  | CMOS Input High Voltage                          |                                                                                                                                                                                                                               | V <sub>CC</sub> - 0.2 | V <sub>cc</sub> + 0.5 | V    |

| V <sub>LC</sub>  | CMOS Input Low Voltage                           |                                                                                                                                                                                                                               | -0.5(3)               | 0.2                   | V    |

| V <sub>OL</sub>  | Output Low Voltage (TTL Load)                    | I <sub>OL</sub> = +2.1 mA, V <sub>CC</sub> = Min                                                                                                                                                                              |                       | 0.45                  | V    |

| V <sub>OH</sub>  | Output High Voltage (TTL Load)                   | $I_{OH} = -0.4 \text{ mA}, V_{CC} = \text{Min}$                                                                                                                                                                               | 2.4                   |                       | V    |

| I <sub>LI</sub>  | Input Leakage Current                            | $V_{CC} = Max$<br>$V_{IN} = GND \text{ to } V_{CC}$                                                                                                                                                                           | -10                   | +10                   | μА   |

| I <sub>LO</sub>  | Output Leakage Current                           | $V_{CC} = Max, \overline{CE} = V_{IH},$ $V_{OUT} = GND \text{ to } V_{CC}$                                                                                                                                                    | -10                   | +10                   | μА   |

| I <sub>SB</sub>  | Standby Power Supply Current (TTL Input Levels)  | $\overline{CE} \ge V_{IH}, \overline{OE} = V_{IL},$ $V_{CC} = Max,$ $f = Max, Outputs Open$                                                                                                                                   | _                     | 5                     | mA   |

| I <sub>SB1</sub> | Standby Power Supply Current (CMOS Input Levels) | $\overline{\text{CE}} \ge \text{V}_{\text{HC}},$ $\text{V}_{\text{CC}} = \text{Max},$ $\text{f} = 0, \text{ Outputs Open},$ $\text{V}_{\text{IN}} \le \text{V}_{\text{LC}} \text{ or V}_{\text{IN}} \ge \text{V}_{\text{HC}}$ | _                     | 150                   | μА   |

| I <sub>cc</sub>  | Supply Current                                   | $\overline{CE} = \overline{OE} = V_{IL},$ $\overline{WE} = V_{IH},$ All I/O's = Open, Inputs = $V_{CC} = 5.5V$                                                                                                                | _                     | 60                    | mA   |

#### Notes:

- Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to MAXIMUM rating conditions for extended periods may affect reliability.

- 2. Extended temperature operation guaranteed with 400 linear feet per minute of air flow.

- 3. Transient inputs with V $_{\rm II}$  and I $_{\rm IL}$  not more negative than -3.0V and -100mA, respectively, are permissible for pulse widths up to 20ns.

- 4. This parameter is sampled and not 100% tested.

## AC ELECTRICAL CHARACTERISTICS—READ CYCLE

$(V_{CC} = 5V \pm 10\%, All Temperature Ranges)^{(2)}$

| Cum               | Doromotor                           | -150 |     | -200 |     | -250 |     | -350 |     | Unit |

|-------------------|-------------------------------------|------|-----|------|-----|------|-----|------|-----|------|

| Sym               | Parameter                           | Min  | Max | Min  | Max | Min  | Max | Min  | Max | Unit |

| t <sub>AVAV</sub> | Read Cycle Time                     | 150  |     | 200  |     | 250  |     | 350  |     | ns   |

| t <sub>AVQV</sub> | Address Access Time                 |      | 150 |      | 200 |      | 250 |      | 350 | ns   |

| t <sub>ELQV</sub> | Chip Enable Access Time             |      | 150 |      | 200 |      | 250 |      | 350 | ns   |

| t <sub>oLQV</sub> | Output Enable Access Time           |      | 80  |      | 100 |      | 100 |      | 100 | ns   |

| t <sub>ELQX</sub> | Chip Enable to Output in Low Z      | 0    |     | 0    |     | 0    |     | 0    |     | ns   |

| t <sub>EHQZ</sub> | Chip Disable to to Output in High Z |      | 55  |      | 60  |      | 65  |      | 70  | ns   |

| t <sub>oLQX</sub> | Output Enable to Output in Low Z    | 0    |     | 0    |     | 0    |     | 0    |     | ns   |

| t <sub>ohqz</sub> | Output Disable to Output in High Z  |      | 55  |      | 60  |      | 65  |      | 70  | ns   |

| t <sub>AVQX</sub> | Output Hold from Address Change     | 0    |     | 0    |     | 0    |     | 0    |     | ns   |

#### TIMING WAVEFORM OF READ CYCLE

# AC CHARACTERISTICS—WRITE CYCLE ( $V_{CC}$ = 5V $\pm$ 10%, All Temperature Ranges)<sup>(2)</sup>

| Symbol                                                    | Parameter           | 150 / 200 | 150 / 200 / 250 / 350 |      |  |  |

|-----------------------------------------------------------|---------------------|-----------|-----------------------|------|--|--|

| Symbol                                                    |                     | Min       | Max                   | Unit |  |  |

| $t_{_{\rm ELRH}}$                                         | Write Cycle Time    |           | 1                     | ms   |  |  |

| t <sub>AVEL</sub>                                         | Address Setup Time  | 10        |                       | ns   |  |  |

| t <sub>ELAX</sub><br>t <sub>WLAX</sub>                    | Address Hold Time   | 50        |                       | ns   |  |  |

| t <sub>WLEL</sub>                                         | Write Setup Time    | 0         |                       | ns   |  |  |

| t <sub>wheh</sub>                                         | Write Hold Time     | 0         |                       | ns   |  |  |

| t <sub>ohel</sub><br>t <sub>ohwl</sub>                    | OE Setup Time       | 10        |                       | ns   |  |  |

| t <sub>whol</sub>                                         | OE Hold Time        | 10        |                       | ns   |  |  |

| t <sub>eleh</sub><br>t <sub>wlwh</sub>                    | WE Pulse Width      | 100       | 1000                  | ns   |  |  |

| t <sub>dveh</sub><br>t <sub>dvwh</sub>                    | Data Setup Time     | 50        |                       | ns   |  |  |

| $\mathbf{t}_{\mathtt{EHDX}}$ $\mathbf{t}_{\mathtt{WHDX}}$ | Data Hold Time      | 10        |                       | ns   |  |  |

| t <sub>ELWL</sub>                                         | CE Setup Time       | 0         |                       | ns   |  |  |

| t <sub>EHWH</sub>                                         | CE Hold Time        | 0         |                       | ns   |  |  |

| t <sub>EHRL</sub><br>t <sub>WHRL</sub>                    | Time to device busy |           | 50                    | ns   |  |  |

## TIMING WAVEFORM OF BYTE WRITE CYCLE (CE CONTROLLED)

## TIMING WAVEFORM OF BYTE WRITE CYCLE (WE CONTROLLED)

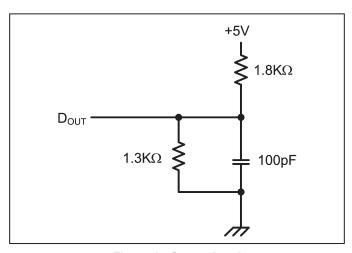

# **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V  |

|-------------------------------|--------------|

| Input Rise and Fall Times     | 10ns         |

| Input Timing Reference Level  | 1.5V         |

| Output Timing Reference Level | 1.5V         |

| Output Load                   | See Figure 1 |

## **TRUTH TABLE**

| Mode           | CE | ŌĒ | WE | I/O              |

|----------------|----|----|----|------------------|

| Read           | L  | L  | Н  | D <sub>out</sub> |

| Write          | L  | Н  | L  | D <sub>IN</sub>  |

| Write Inhibit  | Х  | L  | Х  | _                |

| Write Inhibit  | Х  | Х  | Н  | _                |

| Standby        | Н  | Х  | Х  | High Z           |

| Output Disable | Х  | Н  | Х  | High Z           |

Figure 1. Output Load

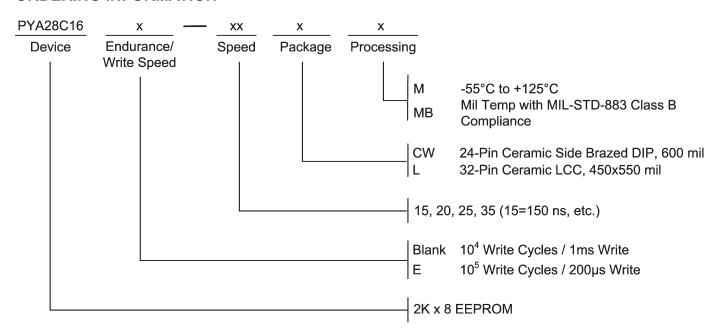

#### ORDERING INFORMATION

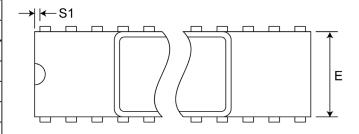

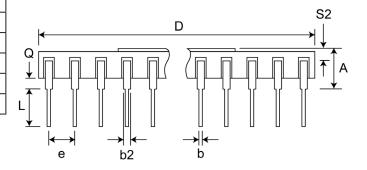

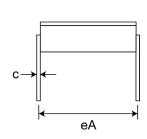

| Pkg #  | C12-1  |         |  |  |

|--------|--------|---------|--|--|

| # Pins | 24 (60 | 00 mil) |  |  |

| Symbol | Min    | Max     |  |  |

| Α      | -      | 0.232   |  |  |

| b      | 0.014  | 0.022   |  |  |

| b2     | 0.045  | 0.065   |  |  |

| С      | 0.008  | 0.014   |  |  |

| D      | -      | 1.290   |  |  |

| Е      | 0.500  | 0.610   |  |  |

| eA     | 0.600  | BSC     |  |  |

| е      | 0.100  | BSC     |  |  |

| L      | 0.125  | 0.200   |  |  |

| Q      | 0.015  | 0.060   |  |  |

| S1     | 0.005  | -       |  |  |

| S2     | 0.005  | _       |  |  |

### SIDE BRAZED DUAL IN-LINE PACKAGE (600 mils)

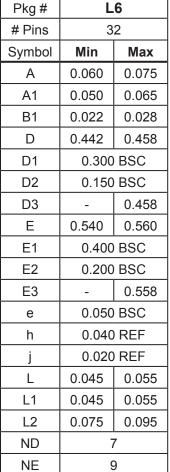

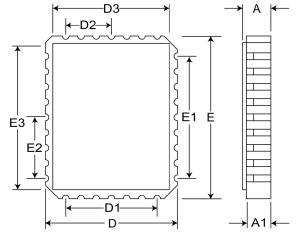

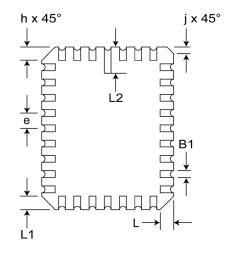

# RECTANGULAR LEADLESS CHIP CARRIER

## **REVISIONS**

| DOCUMENT NUMBER | EEPROM108                |

|-----------------|--------------------------|

| DOCUMENT TITLE  | PYA28C16 - 2K x 8 EEPROM |

| REV | ISSUE DATE | ORIGINATOR | DESCRIPTION OF CHANGE                                   |

|-----|------------|------------|---------------------------------------------------------|

| OR  | Jun 2012   | JDB        | New Data Sheet                                          |

| Α   | Jul 2012   | JDB        | Tightened package definition for 600-Mil Sidebrazed DIP |